## Energy-Band Engineering for Tunable Memory Characteristics through Controlled Doping of Reduced Graphene Oxide

Su-Ting Han,<sup>†</sup> Ye Zhou,<sup>†</sup> Qing Dan Yang,<sup>†</sup> Li Zhou,<sup>†</sup> Long-Biao Huang,<sup>†</sup> Yan Yan,<sup>†</sup> Chun-Sing Lee,<sup>†</sup> and Vellaisamy A. L. Roy<sup>†,‡,\*</sup>

<sup>†</sup>Department of Physics and Materials Science and Center of Super-Diamond and Advanced Films (COSDAF), City University of Hong Kong, Hong Kong, Hong Kong SAR, and <sup>‡</sup>Shenzhen Research Institute, City University of Hong Kong, High-tech Zone, Nanshan District, Shenzhen, China 518057

**ABSTRACT** Tunable memory characteristics are used in multioperational mode circuits where memory cells with various functionalities are needed in one combined device. It is always a challenge to obtain control over threshold voltage for multimode operation. On this regard, we use a strategy of shifting the work function of reduced graphene oxide (rG0) in a controlled manner through doping gold chloride (AuCl<sub>3</sub>) and obtained a gradient increase of rG0 work function. By inserting doped rG0 as floating gate, a controlled threshold voltage (*V*<sub>th</sub>) shift has been achieved in both p- and n-type low voltage flexible memory devices with large memory window (up to 4 times for p-type and 8 times for n-type memory devices) in comparison with pristine rG0 floating gate memory devices. By proper energy band engineering, we demonstrated a flexible floating gate memory device with large memory window and controlled threshold voltage shifts.

**KEYWORDS:** reduced graphene oxide · chemical doping · tunable memory characteristics · increased work function · flexible floating gate memory

n logic circuits, various operational modes are expected to be assembled in a circuit so that multifunctionality is possible within one integrated circuit (IC). Lower threshold voltage  $(V_{th})$  for transistors can be used in noncritical paths to reduce the static power (minimizing overall leakage power), while higher  $V_{\rm th}$  transistors can be used in performance-critical paths to meet performance requirements. In addition, tunable memory characteristics (various V<sub>th</sub> of programmed and erased states) can be utilized in multilevel storage circuits (such as NOR and NAND gate flash) where memory cells with different bits are needed in one combined device. Thus, an adjustable  $V_{th}$  is highly advantageous not only for control over operation mode in logic circuit but also for various data storage applications. In general,  $V_{\rm th}$  of the flash memory device can be tuned via a change in channel conductance by stored charges in floating gate.<sup>1,2</sup> To meet stringent requirements of low power consumption, high integration density and fast access speed, nanofloating gates are considered

as the most promising candidates to replace the planar floating gates for next generation flash memory devices.<sup>3–9</sup> Tuning the memory characteristics by direct energy band engineering of the charge trapping layer has its own niche due to gradient control over the Fermi level of the floating gate. However, the nanofloating gate flash memory based on metal nanoparticles such as gold nanoparticles (Au NPs) could not achieve tunable memory characteristics by energy band engineering due to its fixed Fermi level.<sup>10–13</sup> On this regard, we chose graphene which is a two-dimensional (2D) material with layered structure and its Fermi level can be manipulated.<sup>14</sup> Various methods were proposed to tune the work function of graphene including doping of foreign atoms (boron for p-doping and nitrogen for n-doping),<sup>15,16</sup> dipole moment arising from self-assembled monolayer (SAM) and chemical doping.<sup>17–19</sup> Adsorption-induced chemical doping was considered as an effective way to shift the Fermi level of graphene by charge transfer between the

\* Address correspondence to val.roy@cityu.edu.hk.

Received for review December 19, 2013 and accepted January 28, 2014.

Published online January 28, 2014 10.1021/nn406505t

© 2014 American Chemical Society

VOL.8 • NO.2 • 1923-1931 • 2014

graphene sheets and adsorbed species without introducing substitutional impurities and additional damage to carbon network. On this aspect, gold chloride (AuCl<sub>3</sub>) can be chemically adsorbed to add high work function Au metal on graphene to shift the Fermi level of graphene downward since the positive Au<sup>3+</sup> can be spontaneously reduced to zero charge (Au<sup>0</sup>) by capturing electrons from graphene due to their negative Gibbs free energy.<sup>17–20</sup> There are relatively few reports describing the doping of reduced graphene oxide (rGO).<sup>21</sup> The incompatibility of chemical vapor deposition (CVD) method with high yield and low cost mass production makes rGO become more and more attractive even though unavoidable lattice defects induce slight degradation of its electrical properties.<sup>21</sup> Tremendous progress has been achieved on the fabrication of various kinds of memory devices based on graphene and its derivatives.<sup>23-31</sup> However, tunable memory characteristics by tuning the Fermi level of rGO as floating gate has not been reported elsewhere which is important for various applications such as in multilevel data storage circuits. In addition, we have achieved large memory window (up to 4 times for p-type and 8 times for n-type memory devices) by tuning the Fermi level of rGO through chemical doping which is much wider than our previous reports on Au NPs single floating gate memory device and rGO sheets-Au NPs hybrid double floating gate memory device.<sup>5</sup>

Here, we demonstrate a low voltage flash memory based on AuCl<sub>3</sub> doped self-assembled rGO floating gate on flexible polyethylene terephthalate (PET) substrate. The pentacene and copper hexadecafluorophthalocyanine (F<sub>16</sub>CuPc) were employed as p-type or n-type semiconductors, respectively. By embedding rGO monolayer with various doping concentration of  $AuCl_3$  (as a function of doping time of 0 s, 5 s, 25 and 45 s) between aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) (blocking dielectric layer) and poly(methyl methacrylate) (PMMA) (tunneling dielectric layer), the memory characteristics have been systematically controlled in both p-channel and n-channel memory transistors. Compared with a standard flash memory fabricated on pristine rGO monolayer, the memory window is found to be significantly improved with an increasing doping concentration of AuCl<sub>3</sub>. As the doping time increases to 25 s, a largest memory window is obtained in both p-channel and n-channel flash memory (up to 4 times for p-type and 8 times for n-type memory devices) while increasing the doping time up to 45 s displays rough surface morphology with inferior device performance. X-ray photoemission spectroscopy (XPS) was used to characterize the doping process. Atomic Force microscopy (AFM) was used to examine the surface of the AuCl<sub>3</sub>-doped rGO layer. The change of work function of rGO after metal chloride doping was confirmed by ultraviolet photoemission spectroscopy (UPS). Charge carrier injection

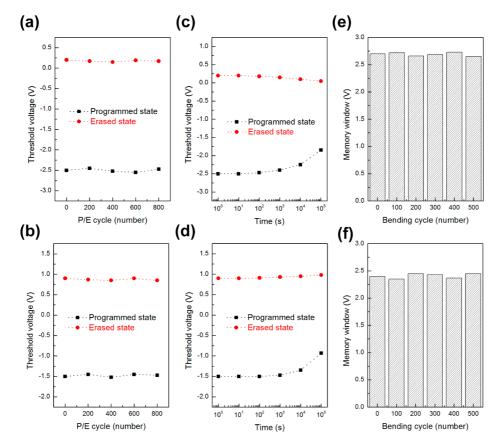

barrier has been lowered through better energy level alignment between the Fermi level of doped rGO layer and HOMO level of pentacene/F<sub>16</sub>CuPc. The downward shift of Fermi level of rGO and increased size and density of reduced Au NPs have a synergistic effect over the significant enhancement of the memory window. Meanwhile, various V<sub>th</sub> have been achieved in both p- and n-type memory devices fabricated on rGO with controlled doping concentration of AuCl<sub>3</sub>. In addition to large memory window and controlled  $V_{\rm th}$ shifts, the chemically doped rGO floating gate memories exhibited fast program/erase speed (100 ms), long retention time (10<sup>5</sup> s), good endurance properties (>800 cycles) and mechanical stability (>500 bending cycles). Furthermore, our fabrication methods including synthesis of rGO sheets, the self-assembly of rGO monolayer and AuCl<sub>3</sub> doping are all solution-processed at low temperature, and have been extended on flexible substrates for the construction of innovative graphene electronics.

### **RESULTS AND DISCUSSION**

Graphite oxide was synthesized from natural graphite (SP-1) by the Hummers method.<sup>32</sup> After converting the graphite oxide to GO by ultrasonication, the well-dispersed negatively charged rGO sheets were achieved by hydrazine reduction of GO with the presence of ammonia in water.<sup>33</sup> The AFM image of single rGO sheet and Raman spectrum evidencing significant structural variation from GO to rGO after the chemical reduction are depicted in the Supporting Information. The rGO sheets display lateral dimension of around  $1-2 \,\mu$ m and an effective thickness of ~1 nm.

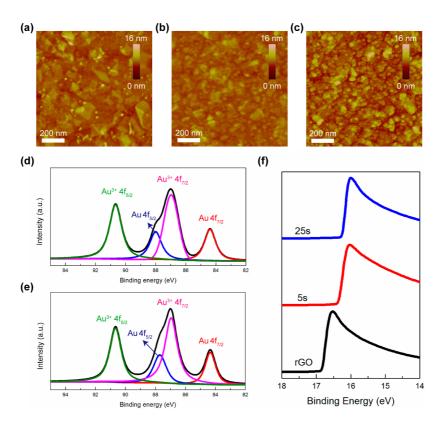

The AFM images indicating the effect of AuCl<sub>3</sub> doping time on the surface morphology of doped rGO and pristine rGO film are shown in Figure 1a-c respectively. The increased size of Au NPs and respective morphological changes could be observed due to longer doping time. Higher reduction potential of  $AuCl_{4}^{-}$  ion than the rGO induces the formation of Au NPs on the rGO film.<sup>18,34</sup> The rGO doped by AuCl<sub>3</sub> for 25 s displayed larger and broader size distribution of Au NPs in comparison with 5 s doping time. However, the rGO doped by AuCl<sub>3</sub> for 45 s displays rough surface morphology (Figure S2) which is not suitable for device fabrication, and the memory devices based on rGO doped by  $AuCl_3$  for 45 s neither have field-effect transistor (FET) properties nor memory performances. Figure 1d,e shows the XPS data of rGO doped with AuCl<sub>3</sub> for 5 and 25 s. The spectral line shape was simulated by a suitable combination of Gaussian and Lorentzian functions to separate the chemical bonding states.<sup>35</sup> For all fitting multiplets, the full width at halfmaximum (fwhm) values was fixed accordingly. The peaks of doped rGO film are composed of metals (Au) and metal ions (Au<sup>3+</sup>), while the corresponding peaks cannot be found in the pristine rGO film (Figure S3 in

ARTICLE

www.acsnano.org

Figure 1. Tapping-mode AFM image of (a) pristine rGO monolayer, (b) rGO doped with AuCl<sub>3</sub> for 5 s, and (c) rGO doped with AuCl<sub>3</sub> for 25 s. The XPS data (metal peak) of (d) rGO doped with AuCl<sub>3</sub> for 5 s and (e) rGO doped with AuCl<sub>3</sub> for 25 s. (f) The work function variance between doped and undoped samples were measured by UPS.

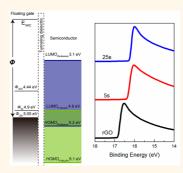

Supporting Information) indicating the successful doping process. For XPS measurements, the samples were prepared on precleaned heavily doped n-type silicon substrates to avoid Au doping effect from the substrate. Simply comparing the peak intensity ratio of Au<sup>3+</sup> to Au cannot confirm the p-doping by electron transfer from rGO sheet to metal ions so that UPS measurements were carried out. Figure 1f shows the UPS spectra around secondary electrons threshold region of pristine rGO film and rGO doped with AuCl<sub>3</sub> for 5 and 25 s. A gold plate is used for the calibration. The vacuum level of the samples were determined by linear extrapolating the secondary electron cutoffs on the high-binding energy side of the UPS spectra (14-18 eV).<sup>36</sup> The work function is determined by subtracting  $E_{SE}$  from  $h\nu$ , where  $h\nu$  and  $E_{SE}$  are the incident photon energy (He I discharge lamp, 21.2 eV) and secondary edge position.<sup>37</sup> The work function of rGO sample is determined to be about 4.44 eV, while the work function of rGO doped with AuCl<sub>3</sub> for 5 and 25 s is found to be 4.9 and 5.05 eV, respectively, demonstrating an increased work function with longer doping duration. The work function of all doped rGO is found to be greater than pristine rGO film indicating that AuCl<sub>3</sub> is a strong p-dopant.

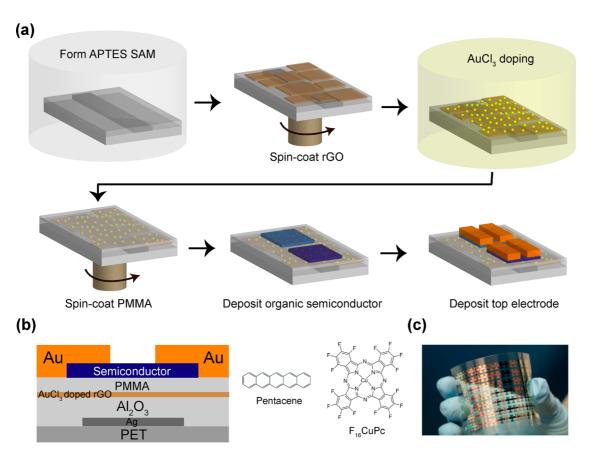

The bottom-gate top-contact flash memory devices were then fabricated on  $AuCl_3$  doped rGO charge trapping layer. The fabrication process is described in Figure 2a. A 25 nm silver (Ag) gate electrode and 40 nm

aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) blocking dielectric layer are successively deposited on the PET substrate by thermal evaporation and atomic layer deposition (ALD), respectively. The positive charged self-assembled monolayer (SAM) is formed by immersing the substrate into a solution of 3-aminopropyltriethoxysilane (APTES). The monolayer coverage with maximum rGO density has been achieved by first-adsorbed rGO pieces followed the Langmuir isotherm mode.<sup>38</sup> The negative charged rGO is allowed to self-assemble for several minutes prior to spin-coating at high speed to form a single layer film (seen in Figure 1a). The substrate with rGO sheets monolayer is then immersed into AuCl<sub>3</sub> aqueous solution with a concentration of 5 mM for various durations (5 and 25 s). After the construction of AuCl<sub>3</sub> doped rGO floating gate, another 25 nm PMMA layer is spin-coated on the floating gate as tunneling dielectric layer. Finally, p-type pentacene/n-type F<sub>16</sub>CuPc and 30 nm Au are thermal evaporated as active layer and source/drain electrodes, respectively. The optical image of the flexible memory is depicted in Figure 2c.

To realize the enhancement of flexibility of flash memory with  $Al_2O_3$  blocking dielectric layer, suitable selection of tunneling dielectric layer is very important. Furthermore, the overall device performance and reliability are determined by tunneling dielectric layer. Here, we choose PMMA as tunneling dielectric layer due to its various advantages such as high resistivity, thermal/mechanical stability, easy processability,

VOL. 8 • NO. 2 • 1923-1931 • 2014

www.acsnano.org

Figure 2. (a) Schematic diagram depicting the basic fabrication process of  $AuCl_3$  doped rGO floating gate memory device. (b) Fabricated device structure for memory device with inserting  $AuCl_3$  doped rGO floating gate and molecular structure of pentacene and  $F_{16}CuPc$ . (c) The optical image of the flexible memory.

compatibility with organic molecule growth and low annealing temperature.<sup>39,40</sup> As the active layer of flash memory, both p-type pentacene and n-type F<sub>16</sub>CuPc were chosen to present the charge trapping effect of AuCl<sub>3</sub> doped rGO floating gate separately. Figure 3a,e shows the transfer characteristics of the standard n-channel and p-channel FET devices without charge trapping layer (device structure: PET/Ag/40 nm Al<sub>2</sub>O<sub>3</sub>/ 25 nm PMMA/pentacene or F<sub>16</sub>CuPc/Au source-drain). Unless otherwise mentioned, the electrical characterization of all the devices was carried out in ambient conditions. The standard devices exhibited negligible charging/discharging behavior after applying the gate bias pulses of -8 V/+8 V for 1 s, indicating almost no charge trapping in the bulk and interfaces of dielectric layers. It is worth noting that APTES has almost no memory effect within short writing time.<sup>1,11</sup> The p-channel standard transistor exhibited a mobility (u) of  $\sim$ 0.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and on/off ratio ( $I_{\rm on}/I_{\rm off}$ ) of  $\sim$ 1  $\times$ 10<sup>4</sup>, while the n-channel standard transistor displayed a  $\mu$  of  $\sim 2 \times 10^{-3}$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $I_{on}/I_{off}$  of  $\sim 2 \times 10^{2}$ .

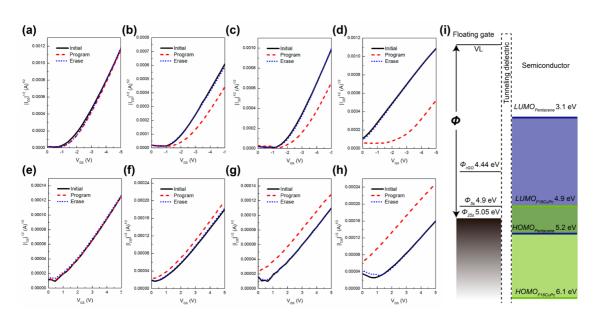

The transfer characteristics of the p-channel memory device (device structure: PET/Ag/40 nm Al<sub>2</sub>O<sub>3</sub>/rGO or doped rGO/25 nm PMMA/pentacene/Au sourcedrain) and n-channel memory devices (device structure: PET/Ag/40 nm Al<sub>2</sub>O<sub>3</sub>/rGO or doped rGO/25 nm PMMA/F<sub>16</sub>CuPc/Au source-drain) at initial state, programmed state and erased state are shown in Figure 3. The transfer curves were obtained by the sweeping of gate voltage after the application of programming/ erasing bias pulses at -8 V/+8 V for 1 s. Charge trapping occurred in the memory transistors after the insertion of pristine rGO or AuCl<sub>3</sub> doped rGO between the PMMA and Al<sub>2</sub>O<sub>3</sub> layers. Direct tunneling (at relatively low voltage) and Fowler-Nordheim (F-N) tunneling (at relatively high voltage) are proposed as the favorable ways to program/erase devices rather than the channel hot electron/hole injection since the low drift velocity are induced by low mobility of pentacene and F<sub>16</sub>CuPc compared with Si-based transistor.<sup>1,41</sup> For the flash memory based on pentacene channel, the transfer curve shifts toward negative voltage direction in comparison with the initial state, which approves that rGO and doped rGO act as trapping element of holes after the application of negative bias at the gate electrode.<sup>1</sup> Controllable V<sub>th</sub> shifts of programmed and erased states strongly influence the memory window  $(\Delta V_{\rm th})$  which is determined by the number of trapped charge carriers in the floating gate and can be defined as the difference between the  $V_{\rm th}$  of programmed state and erased state ( $V_{th}$  (programmed) and  $V_{th}$  (erased)). The memory windows of the p-channel flash memories

VOL. 8 • NO. 2 • 1923-1931 • 2014 A

ARTICLE

Figure 3. (a) Transfer characteristics of a standard p-channel pentacene FET device. Memory characteristics of flash memories based on (b) pristine rGO film, (c) rGO doped with  $AuCl_3$  for 5 s, and (d) rGO doped with  $AuCl_3$  for 25 s. (e) Transfer characteristics of a standard n-channel F<sub>16</sub>CuPc FET device. Memory characteristics of flash memories based on (f) pristine rGO film, (g) rGO doped with  $AuCl_3$  for 5 s, and (h) rGO doped with  $AuCl_3$  for 25 s. (i) Schematic band diagrams of pentacene, F<sub>16</sub>CuPc, and chemical doped rGO.

with the pristine rGO, doped rGO with AuCl<sub>3</sub> for 5 and 25 s as floating gates are 0.7, 1, and 2.7 V, respectively. In the case of rGO based flash memory, the charge carriers are stored in the Fermi level of rGO domains surrounded by the band gap of dielectrics which has similar operation mechanism in comparison with metal NPs floating gate type memory.<sup>3,5</sup> GO can replace rGO layer to work in our device structure to form a chargetrap flash memory in which the charges can be stored in the amorphous GO dielectric where oxygen functionalities like epoxy, carboxyl and hydroxyl groups have high electron affinity.<sup>42</sup> However, the memory characteristics of GO based charge-trap flash memory cannot be manipulated by Fermi level engineering due to its different charge storage mechanism in comparison with the rGO based floating gate flash memory. The narrow memory window of pristine rGO floating gate flash memory may be originated from large charge carrier injection barrier due to the mismatch of the Fermi level of rGO (4.44 eV) and HOMO level of pentacene (5.2 eV). Memory window gradually increased with the increased immersing time and the memory device based on rGO doped AuCl<sub>3</sub> for 25 s floating gate exhibited a relatively broad memory window. These distinctive memory characteristics of the doped rGO memory devices originated from the alignment of energy levels for the charge injection from semiconductor to floating gate. The AuCl<sub>3</sub> doped rGO shows p-doped characteristics, thus reducing injection barrier between its Fermi level and HOMO of pentacene (Figure 3i). It is believed that lower injection barrier is essential for efficient charge transfer and trapping of charges at AuCl<sub>3</sub> doped rGO floating gate

memory device which resulted a large memory window. Besides the work function engineering, doping with Au NPs affects the memory characteristics of the flash memory in several other ways. Primarily, doping of Au NPs can introduce more charge trapping sites that contribute to easier programming operation and large memory window. The charging/discharging behavior can be elucidated by the ionization potential (IP)/electron affinity (EA) of the metals being used.<sup>43</sup> The difference between the IP and EA is the charging energy, which can be calculated by the equation:  $e^2/2C$ . Where the *e* is the fundamental unit of charge and *C* is the capacitance of the particle which is proportional to the diameter of Au NPs. The capacitance of Au NP can be estimated from  $C = 4\pi\varepsilon_0\varepsilon_r r$ , where  $\varepsilon_0$  is permittivity of vacuum,  $\varepsilon_r$  is the dielectric constant surrounding the nanoparticle, and r is the radius of nanoparticle.<sup>2,44</sup> With longer doping duration, larger and broader size distribution of Au particles is observed in rGO film doped with AuCl<sub>3</sub> for 25 s in which the charging energy is smaller than that of rGO film doped with AuCl<sub>3</sub> for 5 s since both EA and IP approach bulk work function as the radius of NPs increases.<sup>2</sup> Second, with limited AuCl<sub>3</sub> doping time, the Au NPs layer is found to be thin; hence, an interface dipole is formed between the rGO and Au NPs, which enhances the charge-injection process.<sup>18</sup> Finally, the number of trapped holes effectively assists the p-doping process of rGO, which leads to the continuous downward shift of rGO Fermi level.<sup>45</sup> All together, we assume that tunable memory characteristics of memory devices based on doped rGO are originated from coactivation of enhanced work function of rGO, increased size and density of Au NPs,

VOL. 8 • NO. 2 • 1923-1931 • 2014

JAI

www.acsnano.org

interfacial dipole formation between Au NPs and rGO film and finally trapped positive charge carriers assisted p-doping of rGO films. In Figure S4, high voltage memory device based on rGO doped with AuCl<sub>3</sub> for 25 s was also fabricated; the memory window is around 40 V (programming/erasing operation of -80 V/+80 V), which is much higher than those reported memory device based on solution-processed GO/rGO.<sup>42,46</sup>

For n-channel flash memory ( $F_{16}$ CuPc as semiconductor layer), interestingly, the transfer curve shifts toward negative voltage direction compared with the initial state implicating that rGO and doped rGO act as trapping element of holes after the application of negative bias on the gate electrode. The memory windows of n-channel flash memory based on rGO,

TABLE 1. Threshold Voltages of Programmed State and Erased States and Memory Windows with Respect to the Various Doping Concentration of AuCl<sub>3</sub> in rGO

|      | pentacene           |                     |               | F <sub>16</sub> CuPc |                     |               |

|------|---------------------|---------------------|---------------|----------------------|---------------------|---------------|

|      | V <sub>th</sub> (P) | V <sub>th</sub> (E) | memory window | V <sub>th</sub> (P)  | V <sub>th</sub> (E) | Memory window |

| rG0  | -2.3 V              | —1.6 V              | 0.7 V         | 0.4 V                | 0.7 V               | 0.3 V         |

| 5 s  | $-2.7~\mathrm{V}$   | $-1.7~\mathrm{V}$   | 1 V           | $-0.3~\mathrm{V}$    | 0.8 V               | 1.1 V         |

| 25 s | $-2.5~\mathrm{V}$   | 0.2 V               | 2.7 V         | $-1.4~\mathrm{V}$    | 1 V                 | 2.4 V         |

and doped rGO with AuCl<sub>3</sub> for 5 and 25 s as floating gates are 0.3, 1.1, and 2.4 V, respectively. The reason for much narrower memory window of n-channel flash memory based on pristine rGO is due to deeper HOMO level of F<sub>16</sub>CuPc (5.9 eV) in comparison with p-type pentacene eventually leads to low charge carrier injection efficiency (Figure 3i). The insertion of AuCl<sub>3</sub> doped rGO as charge trapping layer shows memory characteristics with enhanced memory window for both p-channel and n-channel flash memory. In addition, through doping a control over  $V_{th}$  shift has been obtained. The tunable  $V_{\rm th}$  values of p- and n-channel flash memory based on rGO with various doping concentration of AuCl<sub>3</sub> are summarized in Table 1. The program/erase speed of p-channel and n-channel memory devices based on pristine and doped rGO with 25 s immersing duration are shown in Figure S5 in the Supporting Information. The V<sub>th</sub> shift is enhanced with increasing programming/erasing operation time. More than 100 ms bias pulse is needed to obtain a large memory window. With an additional Au NPs layer on rGO, the memory device based on chemical doped rGO did not exhibit degradation over program/erase speed compared with pristine rGO memory device, since higher density of Au NPs could produce a lower gatecoupling ratio, which refers to the ratio of voltage drop

Figure 4. Endurance characteristics of (a) p-channel and (b) n-channel memory device based on rGO doped with AuCl<sub>3</sub> for 25 s. Data-retention capability as function of the retention time of (c) p-channel and (d) n-channel memory device based on rGO doped with AuCl<sub>3</sub> for 25 s. Mechanical-stability test of flexbile (e) p-channel and (f) n-channel memory device based on rGO doped with AuCl<sub>3</sub> for 25 s.

# ARTICLE

VOL.8 • NO.2 • 1923-1931 • 2014 A

across the tunneling oxide and total voltage across the channel and gate.

Figure 4a,b shows the results of memory cycling endurance test for the p-channel and n-channel flash memory fabricated on doped rGO floating gate with 25 s immersing duration by sequential application of gate biases of -8 and 8 V at  $V_{DS}$  of -5 V (p-channel) and +5 V (n-channel), for a series of processes such as writing, reading, erasing, and reading, respectively. These results show reversible and stable memory-cycle behavior for more than  $\sim$ 800 cycles. Figure 4c,d shows retention characteristics for both p-channel and n-channel flash memory states, where the programmed and erased states have been measured with a time interval of  $10^n$  s after application of gate bias of -8 and 8 V for 1 s, respectively. The  $V_{\rm th}$  values of both programmed and erased states are well maintained for more than 10<sup>5</sup> s. Measurements were carried out to study the  $V_{\rm th}$  variation of programmed and erased states under various bending radius of curvatures.<sup>47</sup> Our memory devices exhibited excellent mechanical properties during the bending test. The measurement on  $V_{\rm th}$  variation of programmed and erased states versus various tensile and compressive bending radii have been included in the Supporting Information (Figure S6). Negligible changes in  $V_{\rm th}$  of programmed and erased states were observed for various bending radii even for a radius as small as  $\sim$ 5 mm. In addition, we recorded  $V_{\rm th}$  of programmed and erased states at various bending cycles under a radius of curvature of 10 mm. Both the p-type and n-type flexible flash memory devices based on AuCl<sub>3</sub> doped rGO with 25 s

#### **METHODS**

**Materials.** The following materials were obtained from Aldrich: auric acid (HAuCl<sub>4</sub>·3H<sub>2</sub>O), graphite powder, 3-aminopropytriethoxysilane (APTES), pentacene and  $F_{16}$ CuPc (sublimated grade). All chemicals and solvents were used without further purification.

Synthesis and Characterization of rG0 Sheets. Graphite oxide was synthesized from graphite by Hummer's method. A total of 12.5 mg as-synthesized graphite oxide was suspended in 25 mL of DI water to create 0.05 wt % brown dispersion. Exfoliation of the graphite oxide to graphene oxide (GO) was achieved by ultrasonication for 1 day. The resulting homogeneous dispersion was mixed with another 25 mL of DI water containing hydrazine (weight ratio of hydrazine to graphene oxide of 7:10) and ammonia. The mixture was refluxed in a water bath around 95 °C for 1 h.

Preparation and Characterization of AuCl<sub>3</sub>-Doped rGO Double Floating Gate. PET substrate with 30 nm Al<sub>2</sub>O<sub>3</sub> was immersed in a solution of APTES (12.5  $\mu$ L of APTES in 10 mL ethanol) for 45 min at room temperature. Excess, nonreacted APTES molecules were removed by rinsing in ethanol three times and dried under nitrogen gas. The positively charged rGO suspension (0.25 mg mL<sup>-1</sup>) was first dispensed onto the modified flexible substrates and allowed to self-assemble for 2 min prior to spincoating at 3000 rpm for 30 s to form rGO monolayer. After rGO monolayer growth, the sample was immersed into AuCl<sub>3</sub> aqueous solution with a concentration of 5 mM for various durations. Then the sample was rinsed with DI water and blow-dried with nitrogen gas. The pristine rGO sheets monolayer and duration exhibited almost no degradation of  $V_{\rm th}$  even after 500 bending cycles as shown in Figure 4e,f.

#### CONCLUSION

In summary, we first presented a low voltage flexible flash memory with tunable memory characteristics based on pristine rGO and chemical doped rGO floating gates. Gradient increase in work function of rGO has been achieved via direct immersion of rGO monolayer into AuCl<sub>3</sub> aqueous solution for various durations. The UPS results show that chemical doping of rGO with AuCl<sub>3</sub> causes the Fermi level down-shift up to 0.6 eV which is attributed to the hole doping process from Au NPs. By proper energy band engineering, a huge enhancement in the memory window has been achieved. With the pristine rGO, doped rGO with AuCl<sub>3</sub> for 5 and 25 s as floating gates, memory windows of 0.7, 1, and 2.7 V for p-channel flash memories and 0.3, 1.1, and 2.4 V for n-channel flash memories have been obtained, respectively. Meanwhile, various  $V_{\rm th}$  can be achieved in both p- and n-type memory devices fabricated on rGO with various doping concentration of AuCl<sub>3</sub>. The coactivation of enhanced work function of rGO, increased size and density of reduced Au NPs, interfacial dipole formation between Au NPs and rGO film and trapped positive charge carriers assisted p-doping of rGO films are proposed to elucidate the tunable memory characteristics of memory devices based on rGO with chemical doping. We believe that AuCl<sub>3</sub> doped rGO based flexible flash memory modules would help to bring future electronics a step closer to controllable device operation modes for practical applications.

doped rGO sheets monolayer were measured using atomic force microscope (AFM, VEECO Multimode V). All photoemission experiments were performed in a VGESCALAB 2201-XL UHV surface analysis system with a base vacuum of  $10^{-10}$  Torr. The samples were prepared onto the heavily doped n-type precleaned silicon substrate outside then transfer into the chamber. For the XPS measurement, a monochromatic Al K $\alpha$ X-ray source (1486.6 eV) was used to study the energy level changes and possible interfacial chemical reactions across the interface. For UPS measurement, a He discharge lamp (21.2 eV) with an instrumental energy resolution of 90 meV as estimated from the Fermi edge of a cleaned Au was used to measure the work function of the samples. For efficient collection of secondary electrons, samples were negatively biased at -5.0 V with respect to ground.

**Device Fabrication.** Memory devices were fabricated on 200  $\mu$ m PET film with 25 nm thermal evaporated Ag as gate electrode. Al<sub>2</sub>O<sub>3</sub> layers were deposited using a Savannah 100 ALD system at a substrate temperature of 80 °C. Details of fabricating p-channel and n-channel flexible flash memories are described in Supporting Information. A 40 nm thick pentacene and 30 nm thick F<sub>16</sub>CuPc were deposited as p-type and n-type semiconductor layer at a rate of 0.1 Å s<sup>-1</sup> under a base pressure of 2 × 10<sup>-6</sup> Torr. Thirty nanometers thick gold electrodes were thermally evaporated through a shadow mask with a channel length (*L*) of 50  $\mu$ m and width (*W*) of 1000  $\mu$ m. The electrical characteristics of all the devices were measured using a Keithley 2612 source meter at room temperature in ambient conditions.

*Conflict of Interest:* The authors declare no competing financial interest.

Acknowledgment. This work was financially supported by Shenzhen Municipality project no. JCYJ20120618115445056, City University of Hong Kong project no. 7002853 and the Research Grants Council of the Hong Kong Special Administrative Region (Project No.T23-713/11).

Supporting Information Available: The AFM image for rGO sheet, Raman spectra of rGO and GO, AFM image of rGO doped with AuCl<sub>3</sub> for 45 s, XPS data (metal peak) of pristine rGO film, the memory characteristics of high voltage device, program/ erase speed of flash memories and threshold voltages with respect to the various bending radius. This material is available free of charge *via* the Internet at http://pubs.acs.org.

#### **REFERENCES AND NOTES**

- Kim, S.-J.; Lee, J.-S. Flexible Organic Transistor Memory Devices. Nano Lett. 2010, 10, 2884–2890.

- Lee, J.-S.; Kim, Y.-M.; Kwon, J.-H.; Shin, H.; Sohn, B.-H.; Lee, J. Tunable Memory Characteristics of Nanostructured, Nonvolatile Charge Trap Memory Devices Based on a Binary Mixture of Metal Nanoparticles as a Charge Trapping Layer. *Adv. Mater.* 2009, *21*, 178–183.

- Hong, A. J.; Song, E. B.; Yu, H. S.; Allen, M. J.; Kim, J.; Fowler, J. D.; Wassei, J. K.; Park, Y.; Wang, Y.; Zou, J.; *et al.* Graphene Flash Memory. *ACS Nano* **2011**, *5*, 7812–7817.

- Chang, H.-C.; Liu, C.-L.; Chen, W.-C. Flexible Nonvolatile Transistor Memory Devices Based on One-Dimensional Electrospun P3HT:Au Hybrid Nanofibers. *Adv. Funct. Mater.* 2013, *23*, 4960–4968.

- Han, S.-T.; Zhou, Y.; Wang, C.; He, L.; Zhang, W.; Roy, V. A. L. Layer-by-Layer-Assembled Reduced Graphene Oxide/Gold Nanoparticle Hybrid Double-Floating-Gate Structure for Low-Voltage Flexible Flash Memory. *Adv. Mater.* 2013, 25, 872–877.

- Han, S.-T.; Zhou, Y.; Xu, Z.-X.; Huang, L.-B.; Yang, X.-B.; Roy, V. A. L. Microcontact Printing of Ultrahigh Density Gold Nanoparticle Monolayer for Flexible Flash Memories. *Adv. Mater.* 2012, *24*, 3556–3561.

- Han, S.-T.; Zhou, Y.; Roy, V. A. L. Towards the Development of Flexible Non-Volatile Memories. *Adv. Mater.* 2013, *25*, 5425–5449.

- Tseng, C.-W.; Huang, D.-C.; Tao, Y.-T. Azobenzene-Functionalized Gold Nanoparticles as Hybrid Double-Floating-Gate in Pentacene Thin-Film Transistors/Memories with Enhanced Response, Retention, and Memory Windows. *ACS Appl. Mater. Interfaces* **2013**, *5*, 9528–9536.

- 9. Tseng, C.-W.; Tao, Y.-T. Electric Bistability in Pentacene Film-Based Transistor Embedding Gold Nanoparticles. J. Am. Chem. Soc. **2009**, *131*, 12441–12450.

- Lee, J.-S.; Cho, J.; Lee, C.; Kim, I.; Park, J.; Kim, Y.-M.; Shin, H.; Lee, J.; Caruso, F. Layer-by-Layer Assembled Charge-Trap Memory Devices with Adjustable Electronic Properties. *Nat. Nanotechnol.* **2007**, *2*, 790–795.

- Han, S.-T.; Zhou, Y.; Xu, Z.-X.; Roy, V. A. L.; Hung, T. F. Nanoparticle Size Dependent Threshold Voltage Shifts in Organic Memory Transistors. J. Mater. Chem. 2011, 21, 14575–14580.

- Lee, J.-S.; Kim, Y.-M.; Kwon, J.-H.; Sim, J. S.; Shin, H.; Sohn, B.-H.; Jia, Q. Multilevel Data Storage Memory Devices Based on the Controlled Capacitive Coupling of Trapped Electrons. *Adv. Mater.* **2011**, *23*, 2064–2068.

- Talapin, D. V.; Lee, J.-S.; Kovalenko, M. V.; Shevchenko, E. V. Prospects of Colloidal Nanocrystals for Electronic and Optoelectronic Applications. *Chem. Rev.* 2009, *110*, 389–458.

- 14. Huang, X.; Qi, X.; Boey, F.; Zhang, H. Graphene-Based Composites. *Chem. Soc. Rev.* **2012**, *41*, 666–686.

- Stephan, O.; Ajayan, P. M.; Colliex, C.; Redlich, P.; Lambert, J. M.; Bernier, P.; Lefin, P. Doping Graphitic and Carbon Nanotube Structures with Boron and Nitrogen. *Science* 1994, *266*, 1683–1685.

- Panchakarla, L. S.; Subrahmanyam, K. S.; Saha, S. K.; Govindaraj, A.; Krishnamurthy, H. R.; Waghmare, U. V.; Rao, C. N. R.

Synthesis, Structure, and Properties of Boron- and Nitrogen-Doped Graphene. *Adv. Mater.* **2009**, *21*, 4726–4730.

- Kwon, K. C.; Kim, B. J.; Lee, J.-L.; Kim, S. Y. Role of Ionic Chlorine in the Thermal Degradation of Metal Chloride-Doped Graphene Sheets. J. Mater. Chem. C 2013, 1, 253–259.

- Shi, Y.; Kim, K. K.; Reina, A.; Hofmann, M.; Li, L.-J.; Kong, J. Work Function Engineering of Graphene Electrode via Chemical Doping. ACS Nano 2010, 4, 2689–2694.

- Kwon, K. C.; Choi, K. S.; Kim, S. Y. Increased Work Function in Few-Layer Graphene Sheets via Metal Chloride Doping. Adv. Funct. Mater. 2012, 22, 4724–4731.

- Das, A.; Pisana, S.; Chakraborty, B.; Piscanec, S.; Saha, S. K.; Waghmare, U. V.; Novoselov, K. S.; Krishnamurthy, H. R.; Geim, A. K.; Ferrari, A. C.; *et al.* Monitoring Dopants by Raman Scattering in an Electrochemically Top-Gated Graphene Transistor. *Nat. Nanotechnol.* **2008**, *3*, 210–215.

- Kang, B.; Lim, S.; Lee, W. H.; Jo, S. B.; Cho, K. Work-Function-Tuned Reduced Graphene Oxide via Direct Surface Functionalization as Source/Drain Electrodes in Bottom-Contact Organic Transistors. Adv. Mater. 2013, 25, 5856–5862.

- Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. Electric Field Effect in Atomically Thin Carbon Films. *Science* 2004, 306, 666–669.

- Park, J. K.; Song, S. M.; Mun, J. H.; Cho, B. J. Graphene Gate Electrode for MOS Structure-Based Electronic Devices. *Nano Lett.* 2011, *11*, 5383–5386.

- Jeong, H. Y.; Kim, J. Y.; Kim, J. W.; Hwang, J. O.; Kim, J.-E.; Lee, J. Y.; Yoon, T. H.; Cho, B. J.; Kim, S. O.; Ruoff, R. S.; *et al.* Graphene Oxide Thin Films for Flexible Nonvolatile Memory Applications. *Nano Lett.* **2010**, *10*, 4381–4386.

- Yu, W. J.; Chae, S. H.; Lee, S. Y.; Duong, D. L.; Lee, Y. H. Ultra-Transparent, Flexible Single-Walled Carbon Nanotube Non-Volatile Memory Device with an Oxygen-Decorated Graphene Electrode. *Adv. Mater.* **2011**, *23*, 1889–1893.

- Chen, Y.; Zhang, B.; Liu, G.; Zhuang, X.; Kang, E.-T. Graphene and Its Derivatives: Switching ON and OFF. *Chem. Soc. Rev.* 2012, 41, 4688–4707.

- Sun, G.; Liu, J.; Zheng, L.; Huang, W.; Zhang, H. Preparation of Weavable, All-Carbon Fibers for Non-Volatile Memory Devices. Angew. Chem., Int. Ed. 2013, 52, 13351–13355.

- Liu, J.; Yin, Z.; Cao, X.; Zhao, F.; Wang, L.; Huang, W.; Zhang, H. Fabrication of Flexible, All-Reduced Graphene Oxide Non-Volatile Memory Devices. *Adv. Mater.* 2013, *25*, 233–238.

- Liu, J.; Yin, Z.; Cao, X.; Zhao, F.; Lin, A.; Xie, L.; Fan, Q.; Boey, F.; Zhang, H.; Huang, W. Bulk Heterojunction Polymer Memory Devices with Reduced Graphene Oxide as Electrodes. *ACS Nano* **2010**, *4*, 3987–3992.

- Yin, Z.; Zeng, Z.; Liu, J.; He, Q.; Chen, P.; Zhang, H. Memory Devices Using a Mixture of MoS<sub>2</sub> and Graphene Oxide as the Active Layer. *Small* **2013**, *9*, 727–731.

- Liu, J.; Lin, Z.; Liu, T.; Yin, Z.; Zhou, X.; Chen, S.; Xie, L.; Boey, F.; Zhang, H.; Huang, W. Multilayer Stacked Low-Temperature-Reduced Graphene Oxide Films: Preparation, Characterization, and Application in Polymer Memory Devices. *Small* **2010**, *6*, 1536–1542.

- Hummers, W. S.; Offeman, R. E. Preparation of Graphitic Oxide. J. Am. Chem. Soc. 1958, 80, 1339–1339.

- Li, D.; Muller, M. B.; Gilje, S.; Kaner, R. B.; Wallace, G. G. Processable Aqueous Dispersions of Graphene Nanosheets. *Nat. Nanotechnol.* 2008, 3, 101–105.

- Shan, B.; Cho, K. First Principles Study of Work Functions of Single Wall Carbon Nanotubes. *Phys. Rev. Lett.* 2005, *94*, 236602.

- Kim, S. Y.; Hong, K.; Lee, J. -L. *In Situ* Determination of Interface Dipole Energy between Tris(8-hydroxyquinoline) Aluminum and MgO Coated Al in Inverted Top-Emitting Organic Light-Emitting Diodes. *Jpn. J. Appl. Phys.* 2011, 50, 101602.

- Seo, J. H.; Yang, R.; Brzezinski, J. Z.; Walker, B.; Bazan, G. C.; Nguyen, T.-Q. Electronic Properties at Gold/Conjugated-Polyelectrolyte Interfaces. *Adv. Mater.* 2009, *21*, 1006–1011.

- Braun, S.; Salaneck, W. R.; Fahlman, M. Energy-Level Alignment at Organic/Metal and Organic/Organic Interfaces. Adv. Mater. 2009, 21, 1450–1472.

- Myung, S.; Park, J.; Lee, H.; Kim, K. S.; Hong, S. Ambipolar Memory Devices Based on Reduced Graphene Oxide and Nanoparticles. *Adv. Mater.* **2010**, *22*, 2045–2049.

- Kim, S.-J.; Park, Y.-S.; Lyu, S.-H.; Lee, J.-S. Nonvolatile Nano-Floating Gate Memory Devices Based on Pentacene Semiconductors and Organic Tunneling Insulator Layers. *Appl. Phys. Lett.* **2010**, *96*, 033302.

- Zhou, Y.; Han, S.-T.; Xu, Z.-X.; Roy, V. A. L. Low Voltage Flexible Nonvolatile Memory with Gold Nanoparticles Embedded in Poly(methyl methacrylate). *Nanotechnology* 2012, 23, 344014.

- Leong, W. L.; Mathews, N.; Tan, B.; Vaidyanathan, S.; Dotz, F.; Mhaisalkar, S. Towards Printable Organic Thin Film Transistor Based Flash Memory Devices. *J. Mater. Chem.* 2011, *21*, 5203–5214.

- Kim, T.-W.; Gao, Y.; Acton, O.; Yip, H.-L.; Ma, H.; Chen, H.; Jen, A. K.-Y. Graphene Oxide Nanosheets Based Organic Field Effect Transistor for Nonvolatile Memory Applications. *Appl. Phys. Lett.* **2010**, *97*, 023310.

- Collier, C. P.; Vossmeyer, T.; Heath, J. R. Nanocrystal Superlattices. Annu. Rev. Phys. Chem. 1998, 49, 371–404.

- Baeg, K.-J.; Noh, Y.-Y.; Sirringhaus, H.; Kim, D.-Y. Controllable Shifts in Threshold Voltage of Top-Gate Polymer Field-Effect Transistors for Applications in Organic Nano Floating Gate Memory. Adv. Funct. Mater. 2010, 20, 224–230.

- Kim, S. M.; Song, E. B.; Lee, S.; Zhu, J.; Seo, D. H.; Mecklenburg, M.; Seo, S.; Wang, K. L. Transparent and Flexible Graphene Charge-Trap Memory. ACS Nano 2012, 6, 7879– 7884.

- Rani, A.; Song, J.-M.; Jung Lee, M.; Lee, J.-S. Reduced Graphene Oxide Based Flexible Organic Charge Trap Memory Devices. *Appl. Phys. Lett.* **2012**, *101*, 233308.

- Zhou, Y.; Han, S.-T.; Xu, Z.-X.; Yang, X.-B.; Ng, H.-P.; Huang, L-B.; Roy, V. A. L. Functional High-k Nanocomposite Dielectrics for Flexible Transistors and Inverters with Excellent Mechanical Properties. J. Mater. Chem. 2012, 22, 14246–14253.